Product Summary

The K7M803625B-QC75 is a 9,437,184 bits Synchronous Static SRAM. The NtRAM, or No Turnaround Random Access Memory utilizes all the bandwidth in any combination of operating cycles. Address, data inputs, and all control signals except output enable and linear burst order are synchronized to input clock. Burst order control of the K7M803625B-QC75 must be tied "High or Low". The K7M803625B-QC75 is implemented with SAMSUNG′s high performance CMOS technology and is available in 100pin TQFP and Multiple power and ground pins minimize ground bounce.

Parametrics

K7M803625B-QC75 absolute maximum ratings: (1)Voltage on VDD Supply Relative to VSS, VDD: -0.3 to 4.6 V; (2)Voltage on Any Other Pin Relative to VSS, VIN: -0.3 to VDD+0.3 V; (3)Power Dissipation, PD: 1.6 W; (4)Storage Temperature, TSTG: -65 to 150 ℃; (5)Operating Temperature: Commercial TOPR: 0 to 70 ℃; Industrial TOPR: -40 to 85 ℃; (6)Storage Temperature Range Under Bias, TBIAS: -10 to 85 ℃.

Features

K7M803625B-QC75 features: (1)I/O Supply Voltage 33V+0165V/-0165V for 33V I/O or 25V+04V/-0125V for 25V I/O; (2)Byte Writable Function; (3)Enable clock and suspend operation; (4)Single READ/WRITE control pin; (5)Self-Timed Write Cycle; (6)Three Chip Enable for simple depth expansion with no data contention ; (7)Α interleaved burst or a linear burst mode; (8)Asynchronous output enable control; (9)Power Down mode; (10)100-TQFP-1420A; (11)Operating in commercial and industrial temperature range.

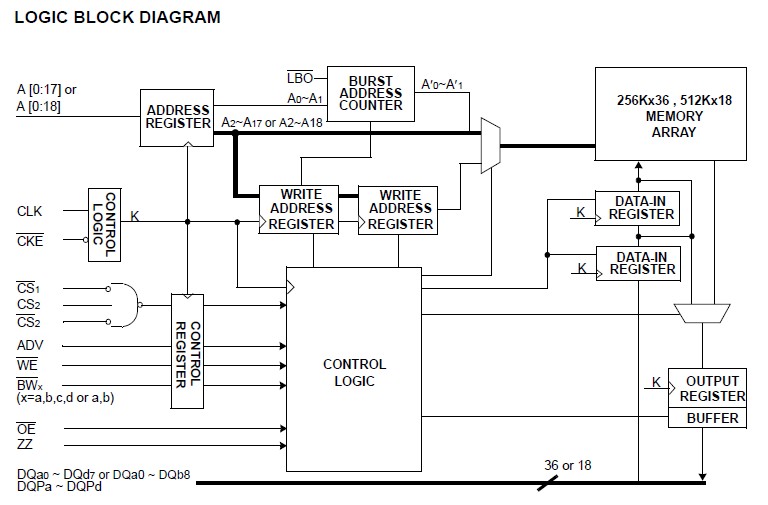

Diagrams

|

K7M801825B |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

K7M803625B |

Other |

|

Data Sheet |

Negotiable |

|

||||

(China (Mainland))

(China (Mainland))